当前位置:首页>> 74ls00设计半加器

半加器

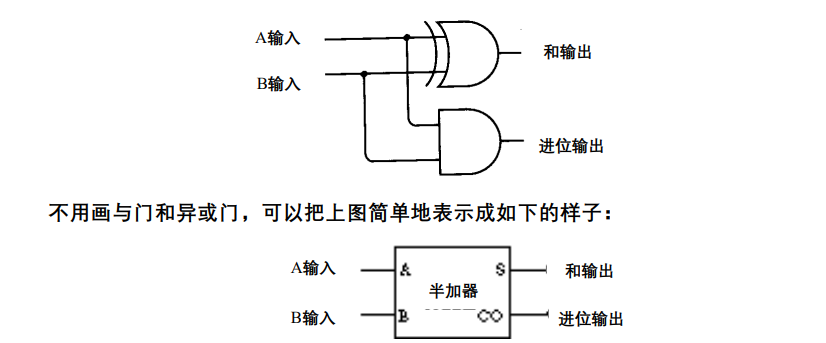

半加器的设计

半加器的介绍

全加器属于组合逻辑电路,主要用于实现二进制加法运算 74ls7418

半加器

半加器的设计

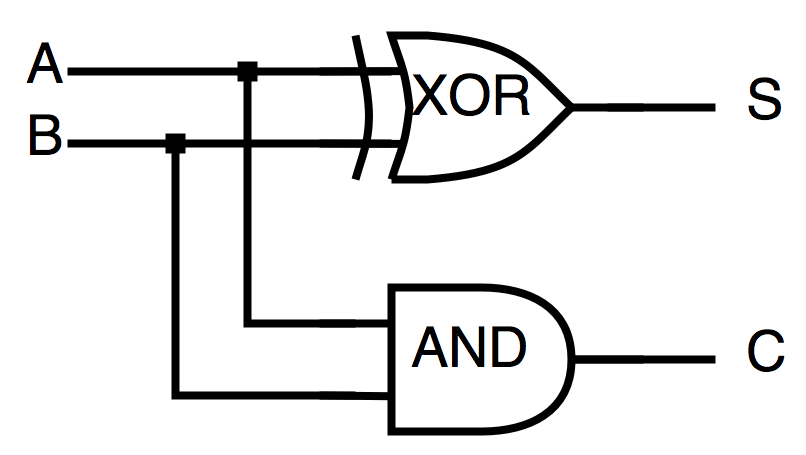

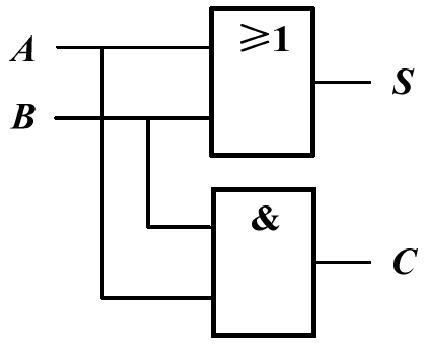

所示为半加器电路图

下面电路中,能实现半加器功能的是

半加器

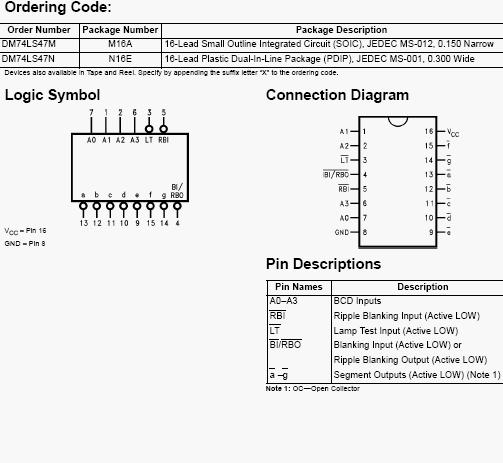

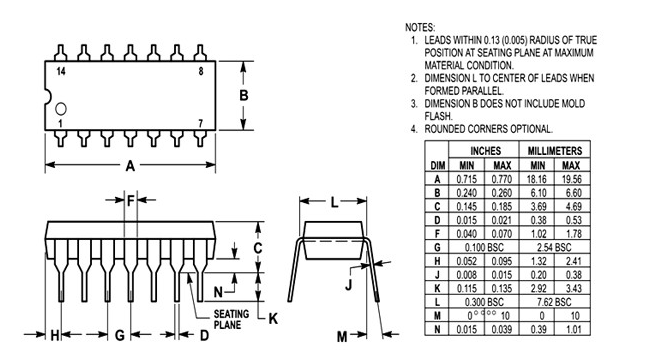

74ls00引脚图及功能真值表和特性参数

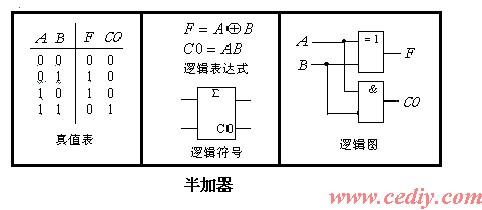

半加器,不考虑来自低位的进位,将两个一位的二进制数 相加 输 0 0

例如,下图是半加器,变量ab无所谓高低位了

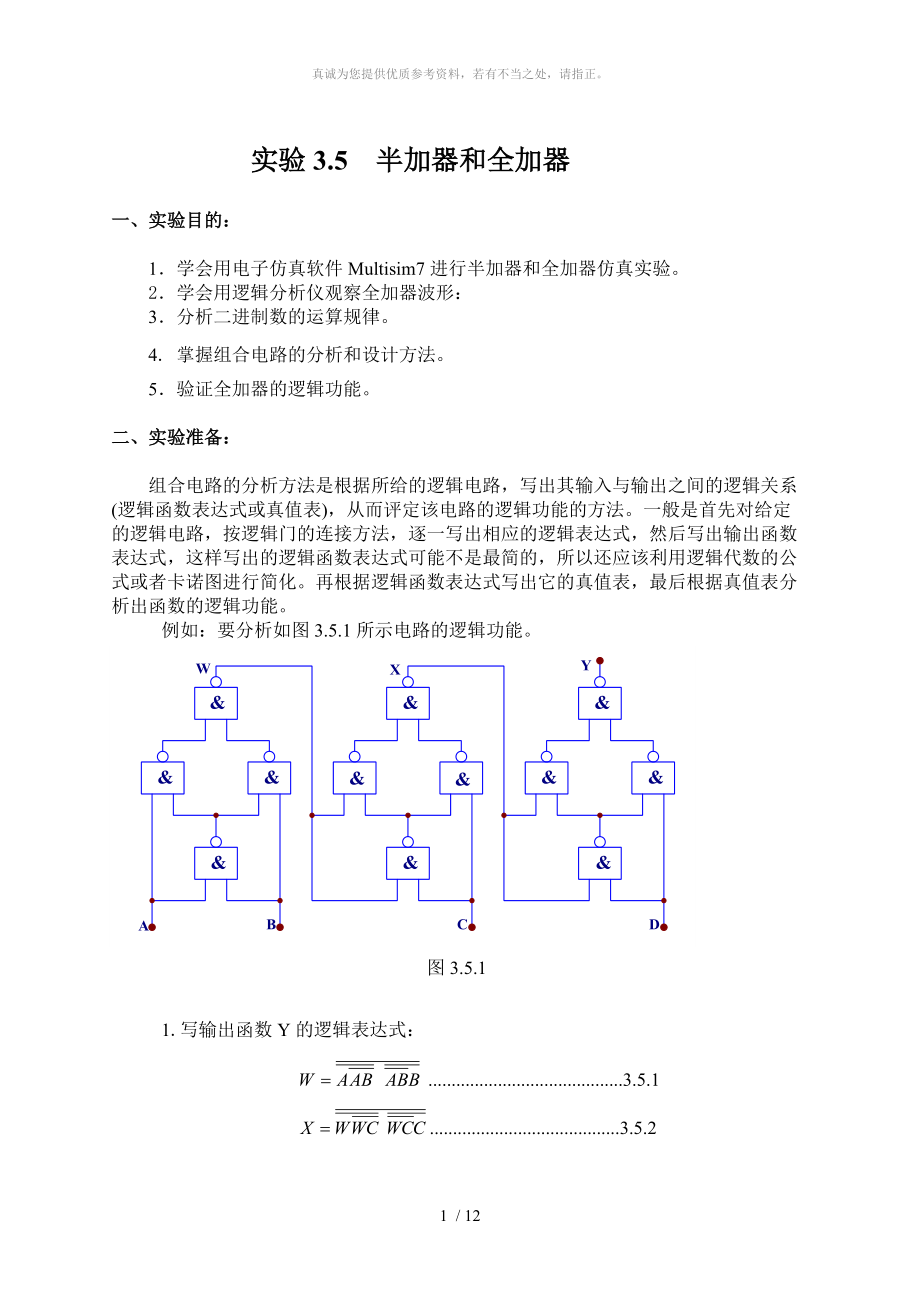

组合逻辑电路的分析半加器和加法器doc5页

半加器

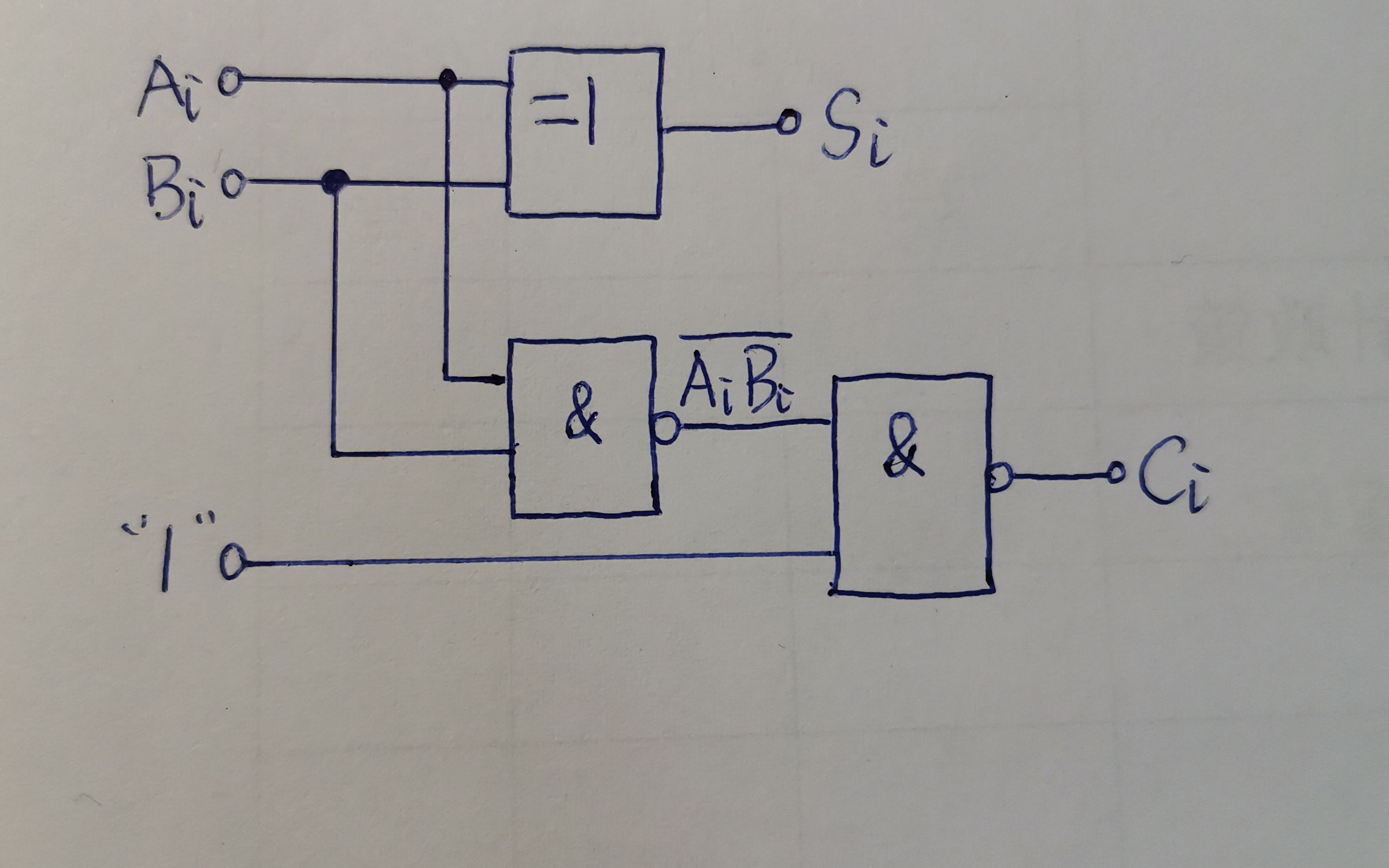

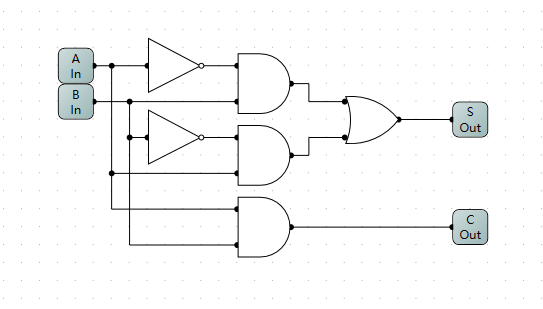

21半加器电路的verilog描述 211半加器的数据流建模描述方式

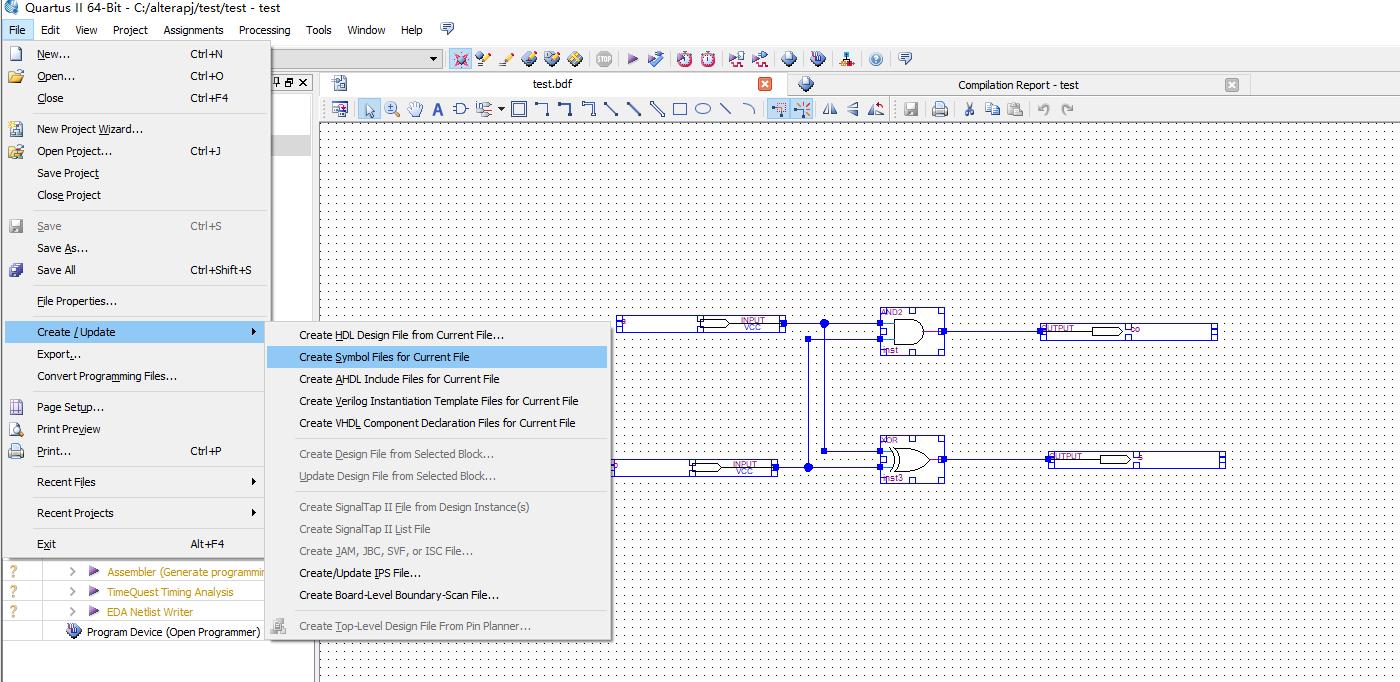

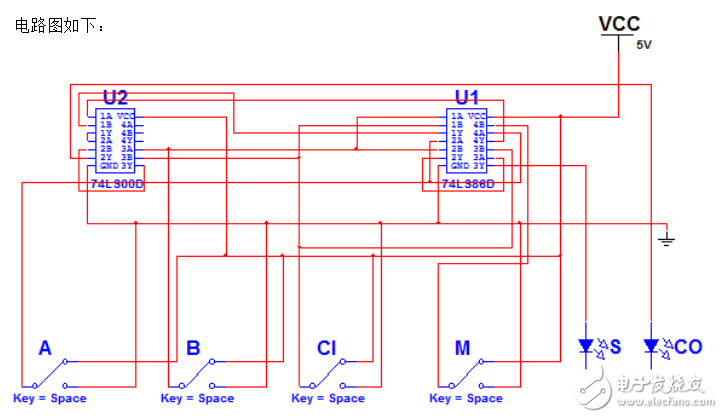

11 门电路组成的半加器仿真

31 行波进位加法器电路图

用74283加法器和逻辑门设计实现一位841bcd码加法器电路,输入输出均为

半加器的电路图

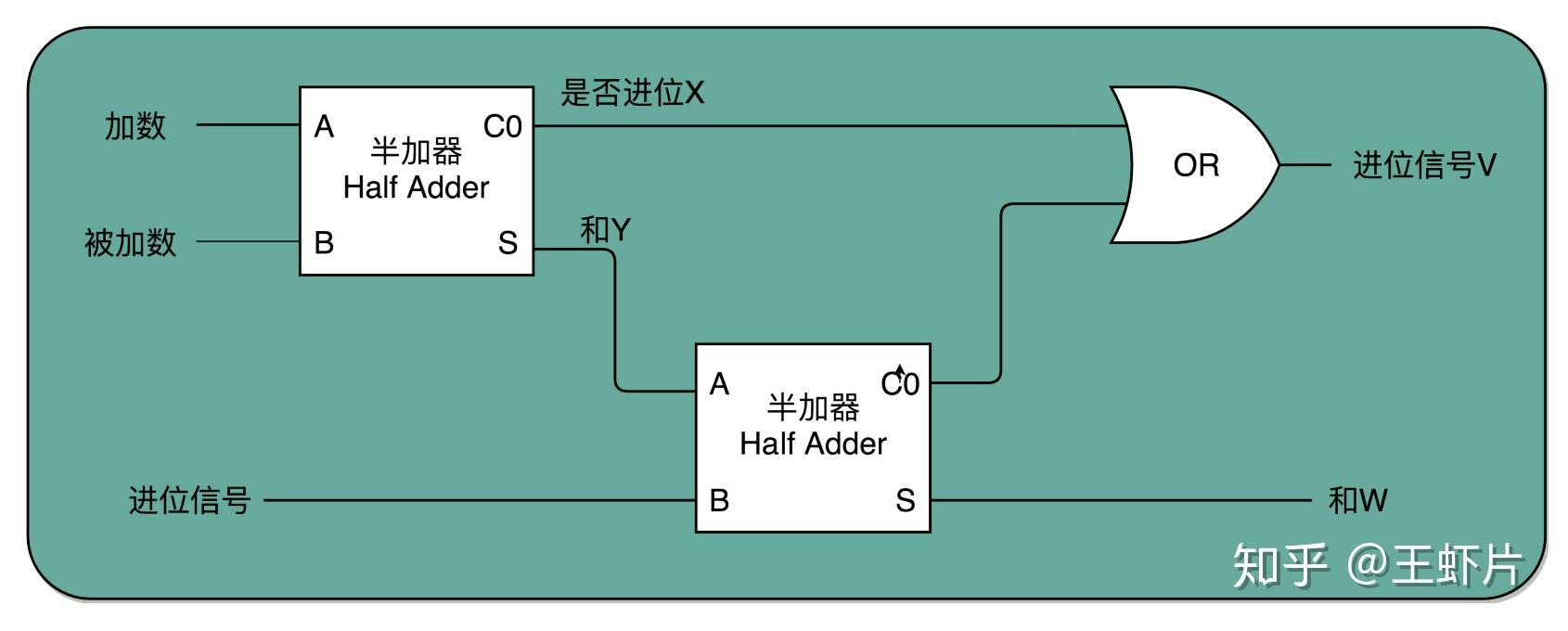

半加器与全加器

两个半加器组成全加器的做法浅谈全加器和半加器的应用

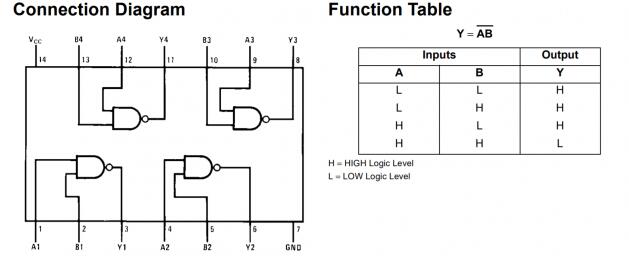

如何使用74ls00和74ls20设计全加器电路

应用74ls139译码器和最少的与非门实现全减器

multisim数电仿真半加器和全加器

实验二组合逻辑电路半加器全加器

设计—加法器实验报告 实验器材 数字电路实验箱,集成电路芯片74ls86

数字电路31半加器与全加器

74ls00

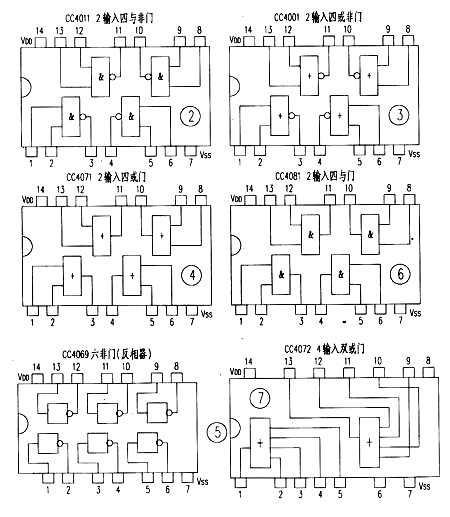

首页 电源技术 设计应用 自制cmos 集成电路测试仪 电子技术的电控

用一片(74ls86)和(74ls00)组成半加器 第1

最近更新的...

更多相关内容:

© 微语生活图库,此页面图片不可商用

微语生活图片下载 使建于2016年,当前更时间:2024-09-28 12:09:23

74ls00设计半加器图片下载